Interconnect Technology

Interconnect Technology

Nextgin Technology is the creator of the VeCS (Vertical Conductive Structure) technique to enable blind structure with high aspect ratio and a tune and shield the properties of the vertical interconnect.

VeCS can be fabricated in current board shop with modern tools for creating, plating and filling slots. No new factories to be build for

The versatility of VeCS depends on your creativity. The sweat spot for the VeCS pitch is around 0,6mm but we can easily reduce the pitch down to smaller number

The new slot generations X-VeCS are focussed on pitch around the 0,15mm mark. The focus is to bring the number of packages in an assembly down to reduce cost of the assembly and also reduce the low of the die to die transmission line. These so called CoWoP applications are growing and VeCS can play an interesting role in opening the door for the PCB industry to play a role in the substrate / combined chip package market.

VeCS

The applications for VeCS focus on thick, high and very high layer count products. Depth capability for processing deep blind slots is important and therefore depth control is a key factor. The next signal layer is typically only a tenth of a millimetre away.

We have introduced a hybrid processing techniques to form the slot mechanical (higher speed and cutting dielectric and copper) and the last section to the signal and bottom GND to be connected using laser ablation. Similar as in Microvia formation the laser stops at the bottom layer.

Tuning the performance of a deep VeCS for 224Gbs application. Using Class 9 materials in a 0,9mm pitch set-up. The differential pair is opposite the shielding and the Electro Magnetic wave is contained by the side wings of the slot (also part of the shielding). In addition we have included extra GND return vias to smooth the Insertion Loss curve. The TDR graph is showing inductive response. Adding pads to the vertical trace balances the inductive effect and flattens the impedance matching the horizontal trace impedance.

Curve C1_3 is the situation before optimization C1_6 is situation after optimization.

With 3D fieldsolvers futher optimizations can be achieved to get to low loss transitions.

Optimizing of the VeCS, C1_1 (green) improved to C1_6 creating less reflective loss. Depending bandwidth requirements the engineer can make the choice to reduce material requirement a class or more down if reflective losses are minimized.

The applications for VeCS focus on thick, high and very high layer count products. Depth capability for processing deep blind slots is important and therefore depth control is a key factor. The next signal layer is typically only a tenth of a millimetre away.

We have introduced a hybrid processing techniques to form the slot mechanical (higher speed and cutting dielectric and copper) and the last section to the signal and bottom GND to be connected using laser ablation. Similar as in Microvia formation the laser stops at the bottom layer.

Tuning the performance of a deep VeCS for 224Gbs application. Using Class 9 materials in a 0,9mm pitch set-up. The differential pair is opposite the shielding and the Electro Magnetic wave is contained by the side wings of the slot (also part of the shielding). In addition we have included extra GND return vias to smooth the Insertion Loss curve. The TDR graph is showing inductive response. Adding pads to the vertical trace balances the inductive effect and flattens the impedance matching the horizontal trace impedance.

Curve C1_3 is the situation before optimization C1_6 is situation after optimization.

With 3D fieldsolvers futher optimizations can be achieved to get to low loss transitions.

Optimizing of the VeCS, C1_1 (green) improved to C1_6 creating less reflective loss. Depending bandwidth requirements the engineer can make the choice to reduce material requirement a class or more down if reflective losses are minimized.

PowerVeCS

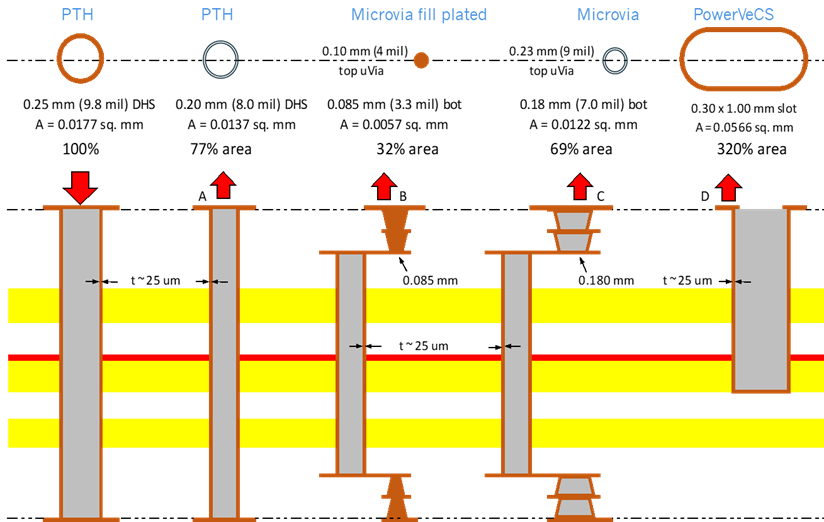

Our definition of PowerVeCS is a slot that is carrying a signal voltage e.g GND, VDD, etc. The idea behind PowerVeCS is to run higher current with lower loss.

PowerVeCS is next to carrying higher currents used for shielding signals. The shape of the PowerVeCS slot is endless. Examples show shapes that can be created. Again, it is down to the creativity of the designer and what the fabricator can built.

The basic shape, SW = Slot Width and SL = Slot Length. The width and length are up to you, what slot width can be formed, plated and filled. For blind slots the depth versus surface area (length and width) determine how deep a blind slot can be formed and processed. To overcome this venting holes can be added in the bottom of the slot that go to the other side of the board. This creates a hydrid (blind and through) VeCS construction. The routing below the slot can still be used except the area of the venting hole. This is in many cases favorable.

We assume the slots are filled and overplated and placed directly under component pads or a combination of pads e.g. GNDs. Combining pads of the same signal can create extra routing space for e.g. signal routing.

Example of slots that have different shapes. Depending design the structures can be adjusted and combined with other interconnect techniques.

Slot formation is not limited to drilling or routing a slot. Slots can be formed using lasers, of Plasma (RIE) or photo-definable dielectrics.